## **Observing and Testing SpaceWire Through PCI and PCI Express**

### Session: SpaceWire Test and Verification

**Short Paper**

Paul E. McKechnie

STAR-Dundee Ltd, c/o University of Dundee, School of Computing, Dundee, DD1 4HN, Scotland, UK

Steve Parkes

# University of Dundee, School of Computing, Dundee, DD1 4HN, Scotland, UK E-mail: paul@star-dundee.com, sparkes@computing.dundee.ac.uk

## ABSTRACT

When testing, validating and verifying systems, monitoring hardware can be used to observe and stimulate the components comprising the system under test. STAR-Dundee is developing the next generation of the SpaceWire PCI board and a SpaceWire PCI Express board to observe and stimulate up to four independent interfaces that implement the SpaceWire protocol. This paper describes the architectures of the Spacewire PCI-3 board and the SpaceWire PCI Express board. It also briefly describes the associated host software and outlines the benefits of these architectures.

## **1** INTRODUCTION

Effective testing requires the ability to accurately monitor the operation of the design under test. Within the SpaceWire application domain, there are several products available for monitoring and stimulating the links that comprise a SpaceWire network. This paper describes two boards that complement the existing products from STAR-Dundee and provide additional functionality to aid the designer while debugging their system. The boards being developed by STAR-Dundee are the next generation SpaceWire PCI board and the SpaceWire PCI Express board [1, 2].

## 2 SPACEWIRE PCI-3

The STAR-Dundee SpaceWire PCI-2 interface card is a test and development platform for the SMCS FPGA device provided by Astrium [3]. The SMCS is designed to be a general purpose interface device but is not suitable for some applications which require high performance and responsiveness between the software running on the PC and the SpaceWire links on the device.

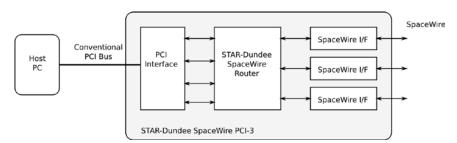

The new STAR-Dundee SpaceWire PCI-3 interface, based on the existing hardware platform, provides new firmware which greatly improves the data transfer capabilities between the host system's software and the SpaceWire interfaces. As illustrated in Figure 1, the PCI Interface provides four bi-directional channels which are directly

Figure 1: Architecture of the SpaceWire PCI-3 board

available to software running on the host PC. Each channel has individual buffering for efficient data transfer. A SpaceWire Router is also present, which adds a routing capability to the PCI card. Packets which are received on a SpaceWire port can be routed to another port or to the PCI interface. The SpaceWire router can also be configured to be bypassed by the SpaceWire interface so the card becomes an easy to use SpaceWire node with 3 interfaces. The extensive configuration capabilities of the SpaceWire router are available in both modes.

#### **3** SPACEWIRE PCI EXPRESS

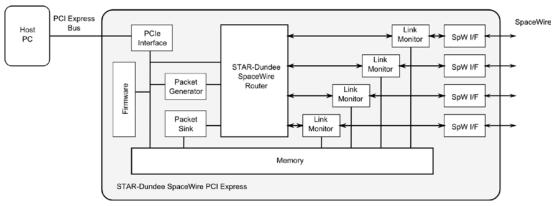

The new SpaceWire PCI Express board supports up to four SpaceWire links and consists of a SpaceWire router, on-board memory, a packet generator, a packet sink, multiple link monitors and upgradeable firmware, as illustrated in Figure 2. The board also employs a Direct Memory Access (DMA) engine for transferring data to the host computer. The maximum theoretical signalling rate for PCI Express is 2.5Gbits per second per lane for a 1<sup>st</sup> generation interface, which translates to 250Mbytes per second of transmitted data. However, the actual achievable data rates will be less due to the protocol overhead and software response time.

The SpaceWire router provides four external ports and several internal interfaces in addition to the configuration interface. The four external ports are fully compliant with the SpaceWire standard [4] and provide direct communication over such links. The internal interfaces provide access to the on-board memory, the host computer and the configuration interface. The on-board memory is accessible over SpaceWire via a hardware packet sink, which records all packets written to it. The host computer can access the board via a device driver, which provides the interface between the host computer and the SpaceWire ports. The internal interfaces are also accessible over the SpaceWire network via the router.

The on-board memory provides storage for all of the link monitors and the packet sink, which allows link activity to be recorded and statistical information to be gathered. The memory also contains an interface to the PCI Express bus so that data can be transferred to the host computer independently from the SpaceWire router. The link monitors can record many events as megabytes of memory are available providing significant temporal visibility.

The packet generator is connected to the SpaceWire router and can send packets to any interface on the router. It is therefore capable of interacting with any component in the SpaceWire network. The packet generator shares some of the functionality provided by the STAR-Dundee Conformance Tester [5] and is compatible with the SpaceWire Validation Software [6]. For example, the packet generator can transmit

Figure 2: Architecture of the SpaceWire PCI Express board

predetermined packets or random data, while scheduling packets for transmission at specific times.

The packet generator can write packets to any interface on the SpaceWire router, which allows the packet generator to write to the packet sink or the connection to the host computer and its associated software driver. This capability is useful for debugging software applications where the rate of incoming data affects the performance and behaviour of the software application.

The packet sink is a SpaceWire interface to the on-board memory, which allows packets to be routed from any of the interfaces available on the SpaceWire router. Although the interface will block due to multiple packets accessing the sink simultaneously, there are no blocking delays caused by software. The operating system of the host computer and its application software are not involved in the operation of the packet sink and do not restrict the ability to receive packets.

The packet sink complements the functionality found in the SpaceWire Validation Software. For example, the sequence number and checksum included within a packet can be verified as they are received. A set of statistics showing the rate at which packets are received and any errors encountered are also made available to the host computer.

The link monitors observe both directions of each external SpaceWire interface while performing two key functions. First, they record packet activity on each of the external SpaceWire interfaces. Second, they capture statistical information from the traffic observed on each external SpaceWire interface. This statistical information includes packet transmission rates, link level events and observed errors.

The link monitors present on the SpaceWire PCI Express board contain a subset of the functionality found in the STAR-Dundee SpaceWire Link Analyser but still provide many features that are beneficial for monitoring and debugging SpaceWire applications [7]. For example, the link monitors record packets entering and leaving the SpaceWire router and can highlight the exit path of each packet. This functionality could be used to verify that packets are being routed correctly.

The PCI Express board uses firmware that can be upgraded in the field. The firmware can provide additional functionality for the SpaceWire router, packet generator, packet sink and link monitors. Most importantly the firmware will be upgradable over

the PCI Express interface, which allows the firmware to be updated from any location where the host computer is accessible.

### 4 HOST SOFTWARE

The SpaceWire PCI Express and SpaceWire PCI-3 devices will have drivers for both Windows and Linux operating systems and will use the new STAR-Dundee driver architecture and API. The new API allows applications to work with any of the STAR-Dundee devices so that applications could potentially work with SpaceWire PCI Express, SpaceWire PCI-3, SpaceWire Router-USB and SpaceWire-USB Brick devices. The new API also provides reusable components to provide features such as Plug and Play (PnP) and RMAP targets and initiators, so the PCI devices can respond to PnP requests [8], for example. STAR-Dundee's existing applications will work with both PCI devices.

## **5** CONCLUSION

This paper has described the architecture of the next generation SpaceWire PCI and SpaceWire PCI Express boards being developed by STAR-Dundee. The benefits of both boards have been presented and the enhanced test capabilities of the SpaceWire PCI Express board have been described.

#### **6 REFERENCES**

- 1. PCI-SIG, "PCI Local Bus Specification", March 2002, http://www.pcisig.com/specifications/conventional/

- 2. PCI-SIG, "PCI Express Base Specification Revision 2.0", 20<sup>th</sup> December 2006, http://www.pcisig.com/specifications/pciexpress/specifications

- 3. STAR-Dundee, "SpaceWire PCI-2", August 2007, available from <a href="http://www.star-dundee.com/">http://www.star-dundee.com/</a>

- 4. ECSS, "SpaceWire Links, nodes, routers and networks", ECSS-E-ST-50-12C, July 2008, available from <u>http://www.ecss.nl</u>.

- 5. S. Parkes and M. Dunstan, "Debugging SpaceWire Devices Using the Conformance Tester", International SpaceWire Conference 2007, Dundee, Scotland, UK, September 2007

- 6. STAR-Dundee, "SpaceWire Validation Software", April 2008, available from <a href="http://www.star-dundee.com/">http://www.star-dundee.com/</a>

- 7. STAR-Dundee, "SpaceWire Link Analyser", August 2009, available from <a href="http://www.star-dundee.com/">http://www.star-dundee.com/</a>

- S. Mills, C. McClements, S.M. Parkes, "STAR-Launch and Network Discovery", International SpaceWire Conference 2010, St. Petersburg, Russia, 22-24 June 2010.